# Design and Evaluation of Nonlinear MPC for Active Load Balancing in Adjacent Battery Cells \*

Ali Arshad Uppal\* Muhammad Rizwan Azam\*

Afaq Ahmed\* Qadeer Ahmed\*\*

\* Department of Electrical and Computer Engineering, COMSATS

University Islamabad, Islamabad, Pakistan 45550 (e-mail:

(ali\_arshad,rizwan.azam)@comsats.edu.pk, ahmadafaq09@yahoo.com)

\*\* Mechanical and Aerospace Engineering, Scott Laboratory 201 W

19th Ave Columbus, OH 43210-1142 (e-mail: ahmed.358@osu.edu)

Abstract: Active load balancing in battery cells has significant advantages in energy storage systems and electric vehicles (EVs). However, diversity in balancing network power electronics components, energy transfer paths, etc., leads to a multitude of architectures and topologies, each yielding varying performance, complexity, and cost. Therefore, this work implements and compares the load balancing performance of (i) series, (ii) module, and (iii) layer-based adjacent battery cell network topologies, each managed by a different nonlinear model predictive control (NMPC) strategy. The solution is built on the dynamics of active balancing networks and battery cells and incorporates high-fidelity balancing currents to characterize the load using state of charge (SOC). The simulation results, which are performed on twelve adjacent cells, reveal that load balancing in cells connected in layer-based topology is achieved in 1430 s. While series and module-based topologies achieved the load balancing objective in 2980 and 2770 s, respectively.

Keywords: Electric vehicle; model predictive control; applications of power electronics; constraint control system; decentralized control

### 1. INTRODUCTION

Forming the backbone of energy storage systems and electric vehicles (EVs), batteries have a critical role to play. Moreover, due to the limited voltage supply of a single cell, they are usually connected in a string of series and parallel configurations to meet the demands of high-end power applications (Qi et al. (2022)). However, this setting usually leads to a charge imbalance among cells that subsequently affects the battery's performance. Therefore, load balancing, which is broadly categorized as active (ALB) and passive balancing, can ameliorate these impacts. Moreover, based on balancing circuits, control schemes, interconnection of cells, and paths of energy transfer, the balancing strategies are further subcategorized into architectures and topologies. Thus this flexibility in design parameters leads to various balancing systems, with each suited for a specific application and yielding different performance, such as balancing time (BT), ease of implementation, computational time, etc. (Ma and Gao (2024)).

Lukasiewycz et al. (2016) provided an automated synthesis framework to formulate a balancing circuit and its control. Ouyang et al. (2024) proposed a hypergraph-based approach in an attempt to unify the modeling for ALB topologies. This scheme facilitated determining the

minimum number of equalizers required for balancing, and by finding a correlation between BT and the graph's Laplacian matrix, they were able to streamline the process of evaluating various topologies. Khan et al. (2024) introduced an H-bridge into a duty cycle balancing (DCB) and cell-to-pack balancing scheme, forming H-DCB, to bypass certain cells in 96 serially connected cell configurations. Using simulation, the authors demonstrated the efficiency of the proposed scheme relative to conventional DCB, achieving 1.5 times faster balancing speed. To reduce the communication and processing overhead, Chatzinikolaou and Rogers (2017) introduced a hierarchical balancing strategy to perform cell balancing and other objectives. By using a decentralized battery management system and multiple control layers, the authors achieved balancing within 2 mV. Similarly, to reduce the architecture's complexity, Wei et al. (2021) employed a constant current strategy to balance the battery's voltages. By using LCC multiresonant as a common equalizer, the proposed work transferred charge from a string of cells to a single cell in an open loop setting. Bani Ahmad et al. (2022) proposed a topology that eliminated the need for balancing three branches of battery systems and reduced it to just a single branch. Their approach involved making use of idle cells, treating them as redundant units that can be dropped while balancing, subsequently leading to lower operational costs. Furthermore, Ghaeminezhad et al. (2021) provided a comparative performance of various topologies, such as

<sup>\*</sup> This work was not supported by any organization.

adjacent, non-adjacent, and mixed topologies, in terms of equalization speed, hardware implementation, economic viability, etc.

In literature, various balancing architectures and topologies have been proposed. For instance, in our previous works Javed et al. (2022) and Javed et al. (2024a), we formulated high-fidelity modeling of four different architectures and performed balancing using a simple control scheme. Therein, we demonstrated that including the dynamic balancing parameters had a significant impact on ALB performance. Similarly, Uppal et al. (2023), and Azam et al. (2024) extended that by using nonlinear model predictive control (NMPC) on buck-boost (BB) architecture and integrating the thermal model, respectively. Therefore, this work aims to integrate the high-fidelity modeling currents into the NMPC framework to evaluate the performance in terms of BT and computational cost for three distinct balancing topologies: series-based cellto-cell (SB), module-based (MB), and layer-based (LB) topologies.

The rest of the paper is organized as follows: Section 2 outlines the mathematical modeling of each topology, and NMPC problem is formulated for ALB in Section 3; the results are discussed in Section 4, and, finally, the paper is concluded in 5.

### 2. MATHEMATICAL MODELING

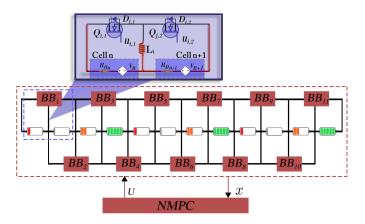

The mathematical models of SB, MB, and LB cell-cell active cell balancing topologies are presented in this section. The atomic unit for all the topologies that balances the SoC levels of two adjacent cells n and n+1 has been depicted in Fig. 1. For transferring charge amongst the cells, a bi-directional BB converter is employed, and the dynamics of a Li-ion cell is represented using a simplified equivalent circuit model (ECM)—an open circuit voltage source  $v_n$  and a resistor  $R_{0_n}$  in series representing the internal resistance of the cell n. The mathematical model of the atomic unit shown in Fig. 1 is given as follows:

### 2.1 Mathematical Model of the Atomic Unit

Fig. 1. Schematic of Series-based topology

The dynamics of SoC levels of the cell n and n+1 are given as

$$\dot{x}_n = \eta_n^{-1} I_{b_n}(x_n, x_{n+1}, u_{i,1}, u_{i,2}),$$

$$\dot{x}_{n+1} = \eta_{n+1}^{-1} I_{b_{n+1}}(x_n, x_{n+1}, u_{i,1}, u_{i,2}),$$

(1)

where  $x_n$ ,  $\eta_n$  and  $I_{b_n}$  represent SoC level, coulombic efficiency and current (A) of the cell n, respectively; and  $u_{i,1}$  and  $u_{i,2}$  are the control inputs, which are duty cycles of MOSFETs  $Q_{i,1}$  and  $Q_{i,2}$  of the BB converter i.

Depending on  $x_n$  and  $x_{n+1}$  the charge transfer between the cells in Fig. 1 is accomplished in the following manner. If  $x_n > x_{n+1}$ ,  $Q_{i,1}$  is turned on using  $u_{i,1}$ , which allows cell n to charge the inductor  $L_i$ . Later, when both MOSFETs are open, a discharging current flows from  $L_i$  to cell n+1through the body diode  $D_{i,2}$ , hence accomplishing the charge transfer from cell n to n + 1. Similarly, when  $x_{n+1} > x_n$ ,  $u_{i,2}$  can be employed to transfer charge in the reverse direction. This transfer of charge from high-SoC cell to low-SoC cell continues until the SoC levels of the cells are balanced. The charging and discharging currents of  $L_i$  are collectively known as balancing currents, which depend upon various static and dynamic parameters of the network in Fig. 1. The following high-fidelity mean balancing current model is used in this work, which is adapted from our earlier work Javed et al. (2024b).

$$\begin{split} I_{c_{i,j}} &= \frac{v_h}{TR_{c_i}} \bigg( u_{i,j} T - t_d + \tau_{c_i} \left( e^{\kappa_i} - 1 \right) \bigg), \\ I_{d_{i,j}} &= \frac{\tau_{d_i} \left( e^{\chi_i} - 1 \right)}{T} \bigg( -I_{p_i} - \frac{a_{0_i} (t_{0_i} - u_{i,j} T)}{\tau_{d_i} \left( e^{\chi_i} - 1 \right)} + 1 \bigg), \quad (3) \\ t_{0_i} &= u_{i,j} T + \tau_{d_i} ln \left( \frac{R_{d_i} v_h}{(v_l + V_{F_{i,j}}) R_{c_i}} \left( 1 - e^{\kappa_i} \right) + 1 \right), \\ \chi_i &= \frac{u_{i,j} T - t_{0_i}}{\tau_{d_i}}, \quad a_{0_i} &= \frac{v_l + V_{F_{i,j}}}{R_{d_i}}. \\ I_{p_i} &= \frac{v_h}{R_{c_i}} \bigg( 1 - e^{\kappa_i} \bigg), \quad \kappa_i &= \frac{t_d - u_{i,j} T}{\tau_{c_i}}, \\ \lambda_i &= \frac{t_d - t}{\tau_{c_i}}, \quad \phi_{i,j} &= \frac{u_{i,j} T - t}{\tau_{d_i}}, \quad R_{d_i} &= R_{0_l} + R_{L_i}, \\ R_{c_i} &= R_{0_h} + R_{L_i} + R_{ds}, \quad \tau_{c_i} &= L_i / R_{c_i}, \quad \tau_{d_i} &= L_i / R_{d_i}, \end{split}$$

where  $I_{c_{i,j}}$  and  $I_{d_{i,j}}$  represent the charging and discharging currents of BB converter i ( $i=1,2,\ldots,N-1$ ) and its MOSFET j (j=1,2);  $v_h=\max(v_n,v_{n+1})$  and  $v_l=\min(v_n,v_{n+1})$ , and  $R_{0_h}$  and  $R_{0_l}$  are the higher and lower open circuit voltages (V) and series resistances ( $\Omega$ ) of two adjacent higher and lower SoC cells, respectively;  $V_{F_{i,j}}$  is the forward voltage drop of diode  $D_{i,j}$  parallel to MOSFET  $Q_{i,j}$  (cf. Fig. 1);  $\tau_c$  and  $\tau_d$  are time constants (s) for charging and discharging of inductor i, respectively;  $I_{p_i}$  is the peak inductor current at  $t=u_{i,j}T$ ;  $t_d$ ,  $t_{0_i}$  and T represent dead time, time instant at which inductor current is zero, and switching time period, respectively; duty cycle of  $Q_{i,j}$  is denoted by  $u_{i,j}$ , and  $L_i$  represents the inductance of the inductor i (H);  $R_{L_i}$ ,  $R_{ds}$ ,  $R_{c_i}$  and  $R_{d_i}$  represent resistances of inductor, on-state switching, and charging and discharging paths of inductor, respectively; and the open circuit voltages of cell n and n+1 are given as

$$v_n = \sum_{s=1}^{8} p_s x_n^{(8-s)}, \quad v_{n+1} = \sum_{s=1}^{8} p_s x_{n+1}^{(8-s)},$$

(4)

where p = [88.56, -320.46, 472.36, -368.96, 166.57, -44.01, 7.18, 2.95].

The expression of current  $I_{b_n}$  of the cell n given in (1) is dependent on the type of adjacent cell balancing topology. The mathematical models of the balancing topologies

for charge equalization of the battery pack consisting of N=12 series connected cells are given in the following subsections.

### 2.2 Series-Based Cell-Cell Topology

To balance the SoC levels of N cells, N-1 BB converters are required, as shown in the zoomed image of Fig. 1. The current of the cell n depends upon its positioning in the battery pack, for instance, the first n=1 and the last n=N cells can only transfer/receive charge to/from cell 2 and cell N-1, respectively. On the other hand, the cell 1 < n < N has two adjacent neighbors, therefore, its net current contains balancing currents of two adjacent BB converters. The total currents of first  $(I_{b_1})$ , n  $(I_{b_n})$  and last  $(I_{b_N})$  cells are characterized as

$$I_{b_{1}}(\boldsymbol{x}, \boldsymbol{u}) = -I_{c_{1,1}}(x_{1}, u_{1,1}) + I_{d_{1,2}}(x_{1}, x_{2}, u_{1,2}),$$

$$I_{b_{n}}(\boldsymbol{x}, \boldsymbol{u}) = -I_{c_{n,1}}(x_{n}, u_{n,1}) - I_{c_{(n-1),2}}(x_{n}, u_{(n-1),2})$$

$$+ I_{d_{(n-1),1}}(x_{n-1}, x_{n}, u_{(n-1),1}) + I_{d_{n,2}}(x_{n}, x_{n+1}, u_{n,2})$$

$$I_{b_{N}}(\boldsymbol{x}, \boldsymbol{u}) = -I_{c_{(N-1),2}}(x_{N}, u_{(N-1),2})$$

$$+ I_{d_{(N-1),1}}(x_{N-1}, x_{N}, u_{(N-1),1}),$$

(5)

where  $n=1,2,\cdots,N$  represents a cell in the battery pack,  $\boldsymbol{x}=\begin{bmatrix}x_1 & x_2 & \cdots & x_N\end{bmatrix}^T$  is the vector representing SoC levels of the cells,  $\boldsymbol{u}=\begin{bmatrix}u_{1,1} & u_{1,2} & \cdots & u_{(N-1),1} & u_{(N-1),2}\end{bmatrix}^T$  is the duty cycle vector.

It is pertinent to mention here that both  $I_{c_{i,j}}$  and  $I_{d_{i,j}}$  in (2) and (3) are positive; however, a negative sign is assigned to  $I_{c_{i,j}}$  in (5). This is due to the current convention followed in this work, according to which a current entering the cell is considered positive, whereas a current going out of a cell is given a negative sign.

# 2.3 Module-Based Cell-Cell topology

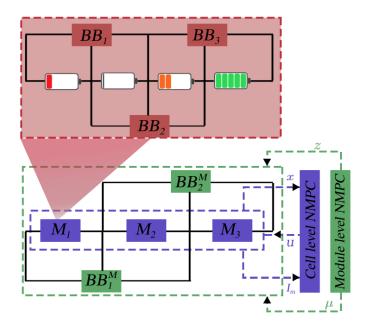

Fig. 2. Schematic of Module-based topology

The total number of cells and the BB converters are similar to the SB cell-cell topology, however, as shown in Fig. 2 the cells are divided into M modules with each module

containing N/M cells. The number of BB converters within a module are N/M-1, and there are M-1 BB converters to equalize the average SoC of each module. This offers increased balancing speed by equalizing the SoC at the cell and module levels. In this topology the net currents of the cells of the battery pack are given as

$$I_{b_1} = -I_{c_{1,1}}(\boldsymbol{x}, \boldsymbol{u}) + I_{d_{1,2}}(\boldsymbol{x}, \boldsymbol{u}) + I_m(\boldsymbol{z}, \boldsymbol{\mu}),$$

(6)

$$I_{b_n} = -I_{c_{n,1}}(\boldsymbol{x}, \boldsymbol{u}) - I_{c_{(n-1),2}}(\boldsymbol{x}, \boldsymbol{u}) + I_{d_{(n-1),1}}(\boldsymbol{x}, \boldsymbol{u}) + I_{d_{n,2}}(\boldsymbol{x}, \boldsymbol{u}) + I_m(\boldsymbol{z}, \boldsymbol{\mu}),$$

(7)

$$I_{b_N} = -I_{c_{(N-1),2}}(\boldsymbol{x}, \boldsymbol{u}) + I_{d_{(N-1),1}}(\boldsymbol{x}, \boldsymbol{u}) + I_m(\boldsymbol{z}, \boldsymbol{\mu}),$$

(8)

$$\boldsymbol{\mu}^T = \begin{bmatrix} \mu_{1,1} & \mu_{1,2} & \dots & \mu_{(M-1),1} & \mu_{(M-1),2} \end{bmatrix}$$

$$\boldsymbol{z}^T = \begin{bmatrix} z_1 & z_2 & \dots & z_M \end{bmatrix}$$

where  $I_m$  represents the current of module  $m \in [1, M]$ , which is given by (7);  $z_m$  is the average SoC of the cells contained in the module m; and  $\mu$  is the duty cycle (control input) vector for module level BB converters.

$$\begin{split} I_{1} &= -I_{c_{1,1}}(z_{1}, \mu_{1,1}) + I_{d_{1,2}}(z_{1}, z_{2}, \mu_{1,2}), \\ I_{m} &= -I_{c_{m,1}}(z_{m}, \mu_{m,1}) - I_{c_{(m-1),2}}(z_{m}, \mu_{(m-1),2}) \\ &+ I_{d_{(m-1),1}}(z_{m-1}, z_{m}, \mu_{(m-1),1}) + I_{d_{m,2}}(z_{m}, z_{m+1}, \mu_{m,2}), \\ I_{M} &= -I_{c_{(M-1),2}}(z_{M}, \mu_{(M-1),2}) \\ &+ I_{d_{(M-1),1}}(z_{M-1}, z_{M}, \mu_{(M-1),1}). \end{split}$$

(7)

# 2.4 Layer-Based Cell-Cell Topology

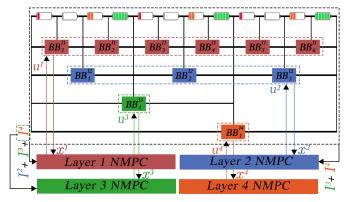

Fig. 3. Schematic of Layer-based topology

In this topology, SoC levels of N cells are equalized by employing  $\lceil \log_2^N \rceil$  layers of BB converters, with each layer containing  $\lfloor N/2^l \rfloor$  equalizers, where  $1 \leq l \leq L-1$  and L represents the total layers in the topology. It is important to note that the last layer has only one BB converter. The net current of the cell n is given as

$$I_{b_{n}} = \sum_{l=1}^{L} \left( \sum_{n_{l}=1}^{2 \times \lfloor N/2^{l} \rfloor} I_{n_{l}}^{l}(\boldsymbol{x}^{l}, \boldsymbol{u}^{l}) \right) + I_{n_{L}}^{L}(\boldsymbol{x}^{L}, \boldsymbol{u}^{L})$$

(8)

$$I_{n_{l}}^{l} = \begin{cases} -I_{c_{r_{l},1}}(u_{r_{l},1}^{l}, x_{n_{l}}^{l}) + I_{d_{r_{l},2}}(u_{r_{l},2}^{l}, x_{n_{l}}^{l}, x_{n_{l}+1}^{l}) \\ -I_{c_{r_{l},2}}(u_{r_{l},2}^{l}, x_{n_{l}}^{l}) + I_{d_{r_{l},1}}(u_{r_{l},1}^{l}, x_{n_{l-1}}^{l}, x_{n_{l}}^{l}) \end{cases},$$

$$I_{n_{L}}^{L} = \begin{cases} -I_{c_{1,1}}(u_{1,1}^{L}, x_{1}^{L}) + I_{d_{1,2}}(u_{1,2}^{L}, x_{1}^{L}, x_{2}^{L}) & 1^{\text{st}} \text{ cell} \\ -I_{c_{1,2}}(u_{1,2}^{L}, x_{2}^{L}) + I_{d_{1,1}}(u_{1,1}^{L}, x_{1}^{L}, x_{2}^{L}) & 2^{\text{nd}} \text{ cell} \end{cases},$$

where,  $n_l$  is odd,  $n_l$  is even and  $I_{n_l}^l$  is the current of cell  $n_l$  in layer l; the duty cycle vector of layer l is given is  $\boldsymbol{u}^l = \{u_{r_l}^l\}$ , where  $r_l = 1, 2, \dots, \lfloor N/2^l \rfloor$ ;  $\boldsymbol{x}^l = \{x_{n_l}^l\}$  with

$n_l = 1, 2, \dots, 2 \times \lfloor N/2^l \rfloor$  represents the SoC vector of layer l; and  $u^L = \begin{bmatrix} u_1^L & u_2^L \end{bmatrix}^T$  and  $x^L = \begin{bmatrix} x_1^L & x_2^L \end{bmatrix}^T$  are duty cycle and SoC vectors of the last layer.

As shown in Fig. 3 there is a dedicated BB converter for each pair of cells in l=1. Whereas, for l>1, each equalizer balances the average SoC levels of cells on its left and right sides. The expression for net current of cell n in (8) might look ambiguous initially; however, from Fig. 3 it can be seen that the current of each layer contributes in  $I_{b_n}$

# 3. NONLINEAR MODEL PREDICTIVE CONTROL DESIGN FOR CELL-CELL TOPOLOGIES

Due to the nonlinearity in the expressions of charging and discharging currents in (2) and (3), the SoC dynamics of cell n (1) are nonlinear; therefore, in the subsequent subsections, the NMPC problem is formulated for balancing the SoC level of cells for the aforementioned topologies.

# 3.1 NMPC Design for Series-Based Cell-Cell Topology

Only one NMPC is required to equalize the SoC levels of the cells in this topology. The optimal control problem in this case is given as

$$\min_{\boldsymbol{x}(\boldsymbol{k}), \boldsymbol{\nu}(\boldsymbol{k})} J(\boldsymbol{x}(\boldsymbol{k}), \boldsymbol{\nu}(\boldsymbol{k})), \qquad (9)$$

$$J = \sum_{k=k_0}^{k_0 + H_p} \sum_{n=1}^{N} \left( x_n(k) - \bar{x}(k) \right)^2, \\

\bar{x}(k) = \frac{1}{N} \sum_{k=0}^{N} x_n(k),$$

subject to

$$x(k+1) - \tilde{f}(x(k), \nu(k)) = 0,$$

(9a)

$$\boldsymbol{x}(k_0) = \boldsymbol{x}_{k_0}, \tag{9b}$$

$$\nu_{i,k} \in [0, 0.4 - t_d/T],$$

(9c)

$$x_n(k) \in [0.05, 0.95],$$

(9d)

$$\nu_{i,1}^T(k)\nu_{i,2}(k) = 0, (9e)$$

where  $\boldsymbol{x}^T(k) = [x_1(k) \ x_2(k) \dots x_N(k)]$  is the vector representing SoC levels of cells;  $\boldsymbol{\nu}(k) = \boldsymbol{u}(k) - t_d/T$ ;  $\boldsymbol{\tilde{f}}$  is the discrete version of  $\boldsymbol{f}^T = [\eta_1^{-1}I_{b_1} \ \eta_2^{-1}I_{b_2} \dots \eta_N^{-1}I_{b_N}]$ ;  $\boldsymbol{x}_{k_0}$  is the vector of current cell's SoC at  $k_0$ ;  $\boldsymbol{\nu}_{i,1}^T(k) = [\nu_{1,1} \ \nu_{2,1} \dots \nu_{N-1,1}]$  and  $\boldsymbol{\nu}_{i,2}^T(k) = [\nu_{1,2} \ \nu_{2,2} \dots \nu_{N-1,2}]$ . The constraint in (9e) is added so that both MOSFETs of a BB converter do not turn on simultaneously.

### 3.2 NMPC Design for Module-Based Cell-Cell Topology

As shown in Fig. 2 there are two levels of NMPC: module-level NMPC, which balances the SoC levels of the module, and cell-level NMPC, which equalizes the cell's SoC levels. The NMPC formulation for both the controllers is given below

$$\min_{\boldsymbol{z}(\boldsymbol{k}), \boldsymbol{w}(\boldsymbol{k})} J(\boldsymbol{z}(\boldsymbol{k}), \boldsymbol{w}(\boldsymbol{k})), \tag{10}$$

$$J = \sum_{k=k_0}^{k_0 + H_p} \sum_{m=1}^{M} \left( z_m(k) - \bar{z}(k) \right)^2,$$

$$\bar{z}(k) = \frac{1}{M} \sum_{k=0}^{N} z_m(k),$$

subject to

$$z(k+1) - \tilde{g}(z(k), w(k)) = 0,$$

(10a)

$$\boldsymbol{z}(k_0) = \boldsymbol{z}_{k_0},\tag{10b}$$

$$w_{i,k} \in [0, 0.4 - t_d/T],$$

(10c)

$$z_n(k) \in [0.05, 0.95],$$

(10d)

$$\mathbf{w}_{i,1}^{T}(k)\mathbf{w}_{i,2}(k) = 0,$$

(10e)

where  $\mathbf{z}^T(k) = [z_1(k) \ z_2(k) \ \dots \ z_M(k)]$  is the vector representing SoC levels of cells;  $\mathbf{w}(k) = \mathbf{\mu}(k) - t_d/T$ ;  $\tilde{\mathbf{g}}$  is the discrete version of  $\mathbf{g}^T = [\eta_1^{-1}I_1 \ \eta_2^{-1}I_2 \ \dots \eta_M^{-1}I_M]$ ;  $\mathbf{z}_{k_0}$  is the vector of module SoC at  $k_0$ ;  $\mathbf{w}_{i,1}$  and  $\mathbf{w}_{i,2}$  are modified control input vectors for the first and second MOSFETs of the module level BB converters.

The cell level NMPC problem formulation in MB cell-cell topology is similar to (9) but the dynamics of the cell represented by f is different-

$$\boldsymbol{f}^T = \begin{bmatrix} \eta_1^{-1} I_{b_1} + I_m & \eta_2^{-1} I_{b_2} + I_m & \cdots \\ \eta_N^{-1} I_{b_N} + I_m & \end{bmatrix},$$

where  $I_m$  is the current of the module that contains the cell.

### 3.3 NMPC Design for Layer-Based Cell-Cell Topology

From Fig. 3 it is evident that there is separate NMPC for each layer. A generalized NMPC formulation for layer l is given as

$$\min_{\boldsymbol{x}^{l}(k), \boldsymbol{\mathcal{U}}^{l}(k)} J^{l}(\boldsymbol{x}^{l}(k), \boldsymbol{\mathcal{U}}^{l}(k)), \tag{11}$$

$$J^{l} = \sum_{k=k_{0}}^{k_{0} + H_{p}} \left[ \sum_{n_{l}=1}^{2 \times \lfloor N/2^{l} \rfloor} \left( x_{n_{l}}^{l}(k) - \bar{x}^{l}(k) \right)^{2} + \sum_{n_{L}=1}^{2} \left( x_{n_{L}}^{L}(k) - \bar{x}^{L}(k) \right)^{2} \right]$$

$$\bar{x}^{l}(k) = \frac{1}{M} \sum_{n_{l}=1}^{2 \times \lfloor N/2^{l} \rfloor} x_{n_{l}}^{l}(k), \quad \bar{x}^{L}(k) = \frac{1}{2} \sum_{n_{L}=1}^{2} x_{n_{L}}^{L}(k),$$

subject to

$$\boldsymbol{x}^{l}(k+1) - \tilde{\boldsymbol{h}}^{l}(\boldsymbol{x}^{l}(k), \boldsymbol{\mathcal{U}}^{l}(k)) = 0, \tag{11a}$$

$$\boldsymbol{x}^l(k_0) = \boldsymbol{x}_{k_0}^l,\tag{11b}$$

$$\mathcal{U}_{n_l,k}^l \in [0, 0.4 - t_d/T],$$

(11c)

$$x_{n_l}^l(k) \in [0.05, 0.95],$$

(11d)

$$\mathcal{U}_{n_l,1}^T(k)\mathcal{U}_{n_l,2}^l(k) = 0,$$

(11e)

where  $\boldsymbol{x}^l$  is the SoC level of cell n for l=1, and for l>1 it represents the average SoC dynamics of the cells on the left and right side of the BB converters (see Fig. 3) in layer l;  $\boldsymbol{\mathcal{U}}^l = \boldsymbol{u}^l - t_d/T$ ; and  $\tilde{\boldsymbol{h}}^l$  is the discrete version of  $\boldsymbol{h}^l$ , which is given as

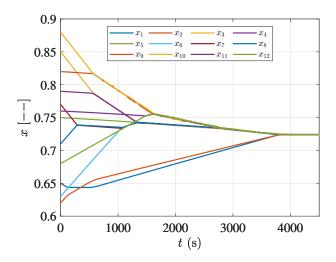

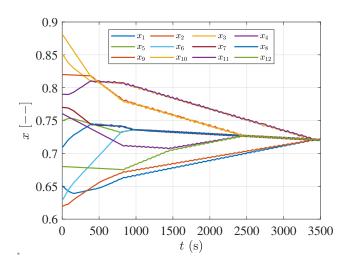

Fig. 4. State of charge for series-based cell-cell topology.

$$\boldsymbol{h}^{l^{T}} = \left[ \eta_{1}^{-1} \sum_{l}^{L} I_{1}^{l} \ \eta_{2}^{-1} \sum_{l}^{L} I_{2}^{l} \ \dots \ \eta_{n_{l}}^{-1} \sum_{l}^{L} I_{n_{l}}^{l} \right]$$

(12)

### 4. RESULTS AND DISCUSSIONS

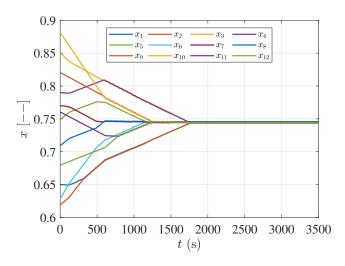

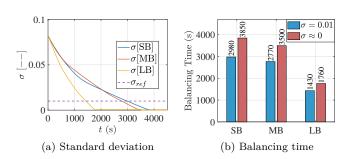

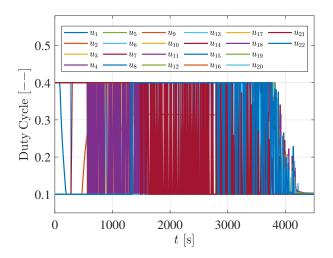

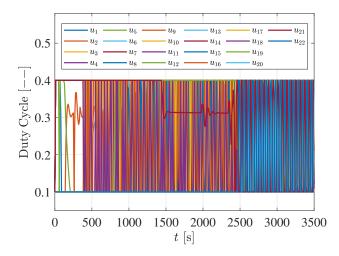

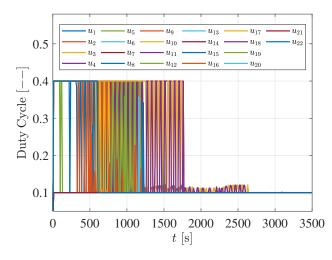

The aim of this work was to evaluate the performance, i.e., BT, of three different topologies using the high-fidelity balancing current within the NMPC framework. We have performed simulations on twelve serially connected cells, the parameters of which are adopted from Uppal et al. (2023). Moreover, the balancing criterion is when the standard deviation of cells' SoC  $\sigma(x)$  becomes equal to 0.01. Figures 4, 5, and 6 depict the evolution of SoC for SB, MB, and LB topologies, respectively. These figures show that for a specific  $x_0$ , all the topologies have been able to equalize the pack. However, their respective BTs vary, as illustrated in Figure 7; for instance, the BTs are 2980, 2770, and 1430 s for SB, MB, and LB topology, respectively. Apart from achieving the fastest balancing, LB topology is also computationally feasible, with a computational time of 360 s; whereas MB and SB took 1800 and 2700 s, respectively, on a Core(TM) i7 CPU @ 1.80 GHz and 16.0 GB of RAM. This is because, for LB topology, the NMPC problem becomes sparse due to a dedicated BB converter for each pair of cells in each layer. Moreover, Figures 8, 9, and 10 show the 22 duty cycles—with 2 for each BB converter—for SB, MB, and LB topologies, respectively.

### 5. CONCLUSION

The future work aims to extend this work by including non-adjacent-based topologies as well as quantifying their impacts at the system level, i.e., range extension of EVs.

### REFERENCES

Azam, M.R., Ahmed, A., Uppal, A.A., and Ahmed, Q. (2024). Nonlinear Model Predictive Control Design for Active Cell Balancing and Thermal Management. In 2024 IEEE Conference on Control Technology and Applications (CCTA), 21–23. IEEE. doi: 10.1109/CCTA60707.2024.10666603.

Fig. 5. State of charge for module-based cell-cell topology.

Fig. 6. State of charge for layer-based cell-cell topology.

Fig. 7. Comparison of the standard deviation of SoCs and balancing time for each topology.

Bani Ahmad, A., Ooi, C.A., Ishak, D., and Abdullah, M.N. (2022). Optimal cell utilisation with state-of-charge balancing control in a grid-scale three-phase battery energy storage system: An experimental validation. *Alexandria Engineering Journal*, 61(11), 9043–9059. doi: 10.1016/j.aej.2022.02.040.

Chatzinikolaou, E. and Rogers, D.J. (2017). Hierarchical Distributed Balancing Control for Large-Scale Reconfigurable AC Battery Packs. *IEEE Trans. Power Electron.*,

Fig. 8. Control input/duty cycle for series topology.

Fig. 9. Control input/duty cycle for module-based topology.

Fig. 10. Control input/duty cycle for layer-based topology.

33(7), 5592–5602. doi:10.1109/TPEL.2017.2782675.

Ghaeminezhad, N., Ouyang, Q., Hu, X., Xu, G., and Wang, Z. (2021). Active Cell Equalization Topologies Analysis for Battery Packs: A Systematic Review. *IEEE Trans. Power Electron.*, 36(8), 9119–9135. doi: 10.1109/TPEL.2021.3052163.

Javed, S.B., Uppal, A.A., Azam, M.R., and Ahmed, Q. (2024a). Model-Based Quantitative Analysis of Power Losses Aware Active Cell Balancing Networks with Load. *IEEE Trans. Transp. Electrif.*, 1. doi: 10.1109/TTE.2024.3455767.

Javed, S.B., Uppal, A.A., Azam, M.R., and Ahmed, Q. (2024b). Model-based quantitative analysis of power losses aware active cell balancing networks with load. *IEEE Transactions on Transportation Electrification*, 1–1. doi:10.1109/TTE.2024.3455767.

Javed, S.B., Uppal, A.A., Azam, M.R., Shehzad, K., and Ahmed, Q. (2022). Model-Based Quantitative Analysis of a Capacitive Cell Balancing Technique using SoC Estimator. In 2022 IEEE Conference on Control Technology and Applications (CCTA), 23–25. IEEE. doi: 10.1109/CCTA49430.2022.9966110.

Khan, N., Ooi, C.A., Shreasth, Alturki, A., Desa, M.K.M., Amir, M., Ahmad, A.B., and Ishak, M.K. (2024). A novel active cell balancing topology for serially connected Li-ion cells in the battery pack for electric vehicle applications. *Sci. Rep.*, 14(18600), 1–21. doi: 10.1038/s41598-024-68226-9.

Lukasiewycz, M., Kauer, M., and Steinhorst, S. (2016). Synthesis of Active Cell Balancing Architectures for Battery Packs. *IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.*, 35(11), 1876–1889. doi: 10.1109/TCAD.2016.2531049.

Ma, Z. and Gao, F. (2024). Topologies and control for battery balancing applications. In Control of Power Electronic Converters and Systems, volume 4, 355–382. Academic Press, Cambridge, MA, USA. doi:10.1016/B978-0-323-85622-5.00008-0.

Ouyang, Q., Ghaeminezhad, N., Li, Y., Wik, T., and Zou, C. (2024). Hypergraph-Based Unified Model Development for Active Battery Equalization Systems. In 2024 American Control Conference (ACC), 10–12. IEEE. doi: 10.23919/ACC60939.2024.10644271.

Qi, X., Fang, M., Wang, Y., Wang, Y., and Chen, Z. (2022). An Equalization Current Ripple Cancellation (ECRC) Converter-Based Centralized Equalization System for Series-Connected Battery Strings. *IEEE Trans. Transp. Electrif.*, 9(2), 2765–2777. doi: 10.1109/TTE.2022.3220932.

Uppal, A.A., Javed, S.B., and Ahmed, Q. (2023). Power Losses Aware Nonlinear Model Predictive Control Design for Active Cell Balancing. *IEEE Control Syst. Lett.*, 7, 3705–3710. doi:10.1109/LCSYS.2023.3342550.

Wei, Z., Peng, F., and Wang, H. (2021). An LCC-Based String-to-Cell Battery Equalizer With Simplified Constant Current Control. *IEEE Trans. Power Electron.*, 37(2), 1816–1827. doi:10.1109/TPEL.2021.3102627.